Parallel Input Serial Output Shift Register Verilog Code

- Parallel Input Serial Output Shift Register Verilog Code

- Parallel Input Serial Output Shift Register Verilog Codes

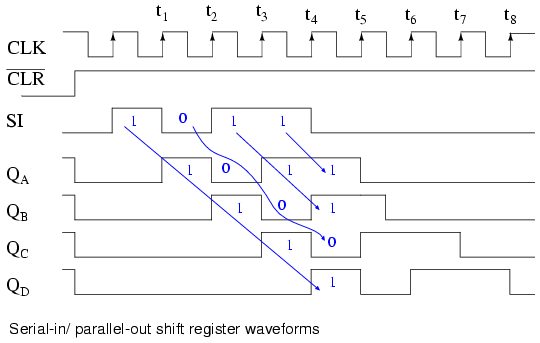

Jan 4, 2014 - Here i have given verilog code for ALU,and all shift registers. SISO: module siso(clk,rst,a,q). Input clk,rst. Parallel-in/ serial-out shift registers do everything that the previous serial-in/ serial-out shift registers do plus input data to all stages simultaneously.

I am learning and practicing Verilog HDL. I wanted to design a 16 bit parallel in series out shift register.

I wrote this code and tried to simulate it.

simulation_resultI could not understand the reason why data output (dout) signal is always LOW

1 Answer

Parallel Input Serial Output Shift Register Verilog Code

It works for me.

Parallel Input Serial Output Shift Register Verilog Codes

BUT!

That code can no be turned into gates.You must use 'posedge clk' or 'negedge clk'. Also your load is a-synchronous which is very unusual and cangive race conditions against the clock edge.

Furthermore it is usual to have a reset condition. As long as there is no 'load' signal the dout will produce X-es. This can very much upset the rest of your circuit. Also you have an extra clock delay in dout. You could, if you want, save a clock cycle there. Here its is with an a-synchronous active low reset: